2. Master synchronization (DCM)

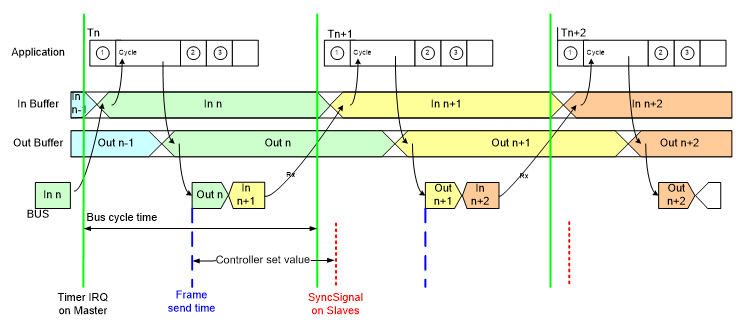

In applications like motion control it is necessary that process data update and the slave SYNC pulses are correlated in timely behavior, because otherwise the SYNC Interrupt (on slave) used to apply new process data to the application would use new data on some slaves and old data on some other in case the current cyclic datagram (which updates process data) is on the flow during the SYNC Interrupt is raised on all slaves at the same time.

The Distributed Clocks Master Synchronization (DCM) provides a controller mechanism to synchronize the process data update and the SYNC pulse in slaves.

The DC Master synchronization (DCM) in BusShift mode adjusts the bus time register of the DC reference clock. All the DC slaves converge to this time. This mode is useful to synchronize multiple EtherCAT busses or if adjustment of Master timer is not possible.

Features:

PI drift controller

Automatic timer adjustment error determination (I controller)