5.1. Link Layer initialization

The different Link Layer modules are selected and parameterized by a Link Layer specific structure. Each Link Layer specific structure start with a common EC_T_LINK_PARMS structure, followed by some Link Layer specific members. The common link parameter structure is passed to EC_T_INIT_SIMULATOR_PARMS::pLinkParms with the call of esInitSimulator() like in the following example:

/* identify Link Layer in the common struture */

oLinkParmsSockRaw.linkParms.dwSignature = EC_LINK_PARMS_SIGNATURE_SOCKRAW;

oLinkParmsSockRaw.linkParms.dwSize = sizeof(EC_T_LINK_PARMS_SOCKRAW);

OsStrncpy(&oLinkParmsSockRaw.linkParms.szDriverIdent, EC_LINK_PARMS_IDENT_SOCKRAW, EC_DRIVER_IDENT_MAXLEN);

/* specific Link Layer parameters should be set here */

/* pass Link Layer parameters */

oInitMasterParms.dwSignature = ATECAT_SIGNATURE;

oInitMasterParms.dwSize = sizeof(EC_T_INIT_MASTER_PARMS);

oInitMasterParms.pLinkParms = &oLinkParmsSockRaw.linkParms;

/* more parameters should be set here */

/* initialize master */

emInitMaster(dwInstanceId, &oInitMasterParms);

-

struct EC_T_LINK_PARMS

Public Members

-

EC_T_DWORD dwSignature

[in] Signature of the adapter specific structure containing the EC_T_LINK_PARMS structure

-

EC_T_DWORD dwSize

[in] Size of the adapter specific structure containing the EC_T_LINK_PARMS structure

-

EC_T_LOG_PARMS LogParms

[in] Logging parameters

-

EC_T_CHAR szDriverIdent[EC_DRIVER_IDENT_NAMESIZE]

[in] Name of Link Layer module (driver identification) for Link Layer Selection

-

EC_T_DWORD dwSignature

5.1.1. Link Layer instance selection via PCI location

For some operating systems it is possible to address the Link Layer instance using its PCI address as an alternative. To do this, EC_LINKUNIT_PCILOCATION (0x01000000) and the PCI location must be set as EC_T_LINK_PARMS::dwInstance.

On Linux the PCI address can be shown using e.g.:

lspci | grep Ethernet

00:19.0 Ethernet controller: Intel Corporation Ethernet Connection I217-LM (rev 04)

04:00.0 Ethernet controller: Intel Corporation 82574L Gigabit Network Connection

05:00.0 Ethernet controller: Intel Corporation 82574L Gigabit Network Connection

The format of EC_T_LINK_PARMS::dwInstance using PCI bus address is:

- 0x01bbddff

bb Bus Number

dd Device Number

ff Function Number

EC_T_LINK_PARMS::dwInstance = 0x01001900; //"0000:00:19.0"

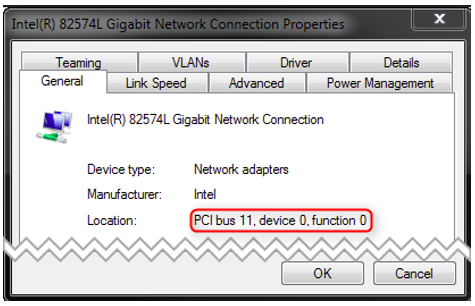

On Windows the integer value displayed in properties dialog must be converted to HEX. E.g the number from the following dialog (PCI bus 11, device 0, function 0) corresponds to 0x010B0000 (bus 0x0B).