5. Link Layer

The EtherCAT master stack currently supports a variety of different Link Layer modules, each of which contained in a single library file, which is loaded by the core library dynamically. The EtherCAT master stack shipment consist of a master core library (e.g. EcMaster.dll for Windows, libEcMaster.a for Linux) and one (or more) libraries each containing support for one specific Link Layer module. Which library actually is loaded, is depending on the Link Layer parameters at runtime.

The principle of the Link Layer selection is that the Link Layer name (Link Layer identification) is used to determine the location and name of a registration function called by the EtherCAT master and registers function pointers that allow access to the Link Layer functional entries.

The EtherCAT Link Layer will be initialized using a Link Layer specific configuration parameter set.

A pointer to this parameter set is part of the master’s initialization settings when calling the function emInitMaster()

The EtherCAT master supports two Link Layer operating modes. If the Link Layer operates in interrupt mode all received Ethernet frames will be processed immediately in the context of the Link Layer receiver task. When using the polling mode the EtherCAT master will call the Link Layer receiver polling function prior to processing received frames.

Optimized Link Layer drivers

Optimized means operating directly on the network device’s register set instead of using the operating system’s native driver.

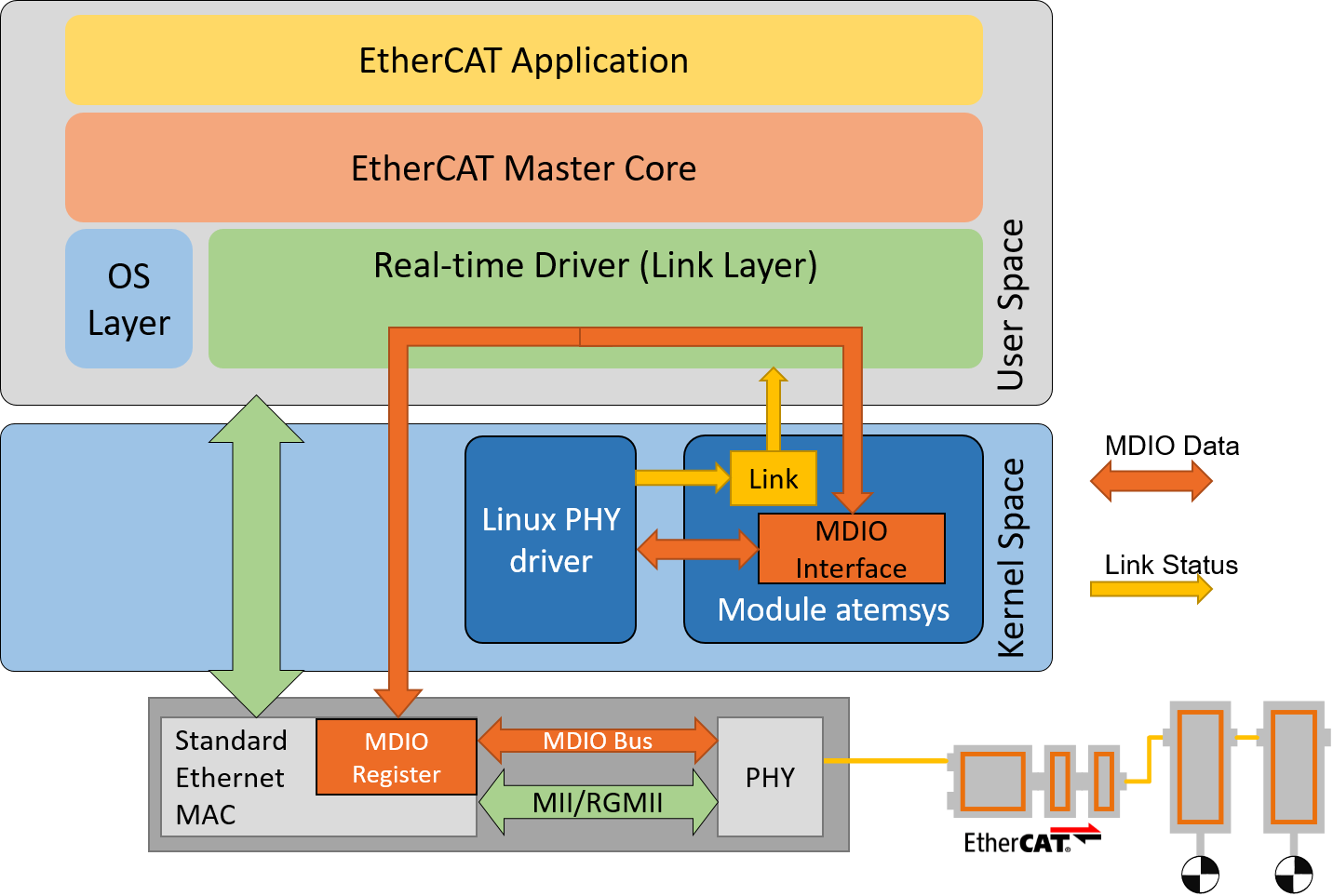

Optimized Link Layer drivers and PHY OS Driver

Some operating systems, e.g. Linux and Xenomai, provide drivers for most common Ethernet controllers and their related physical transceivers (PHY). The manufacturer specific PHY circuits can be handled by a dedicated driver. Using the PHY OS Driver interface it is possible to use the manufacturer’s dedicated PHY driver without modification of the acontis optimized Link Layer driver. Depending on the hardware architecture, an additional module from acontis, e.g. atemsys for Linux, grants access to the MDIO bus to the OS drivers, or request MDIO operations from the OS drivers.

Note

Link Layer modules not listed here may be available if purchased additionally. Not all Link Layer modules support interrupt mode.